# **TMU3130**

## USER MANUAL Preliminary Rev D1.1

## Amendment History

D1.1 2012/09/04 Add DM(PB2)/DP(PB3) F/W setting description, modify Vih

## Information

tenx reserves the right to change or discontinue the manual and online documentation to this product herein to improve reliability, function or design without further notice. tenx does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. tenx products are not designed, intended, or authorized for use in life support appliances, devices, or systems. If Buyer purchases or uses tenx products for any such unintended or unauthorized application, Buyer shall indemnify and hold tenx and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that tenx was negligent regarding the design or manufacture of the part.

## **SPEC Overview**

#### **Microcontroller Features Table**

| CDU  | DOM   |       |               | Instr | ruction | Stack | Interrupt | <b>T</b> : | IVD   |

|------|-------|-------|---------------|-------|---------|-------|-----------|------------|-------|

| CPU  | KOM   |       |               | Set   | Time    | level | vector    | Timers     | LVR   |

| RISC | Flash | 160   | Crystal 6 MHz | 37    | эт      | Q     | 17        | TA/T1      | 2.037 |

| RISC | 8k*14 | + 128 | IRC 48 MHz    | 57    | 2T      | 8     | 17        | T0/T1      | 2.0V  |

#### **IRC Frequency Features Table**

| Operation<br>Frequency        | Internal RC<br>48 MHz | 12 MHz    | 6 MHz     | 3 MHz  | 1.5 MHz |

|-------------------------------|-----------------------|-----------|-----------|--------|---------|

| Battery mode<br>(Stand alone) | +/- 3%                | +/- 3%    | +/- 3%    | +/- 3% | +/- 3%  |

| USB mode<br>(USB Plug in)     | +/- 0.25%             | +/- 0.25% | +/- 0.25% |        |         |

#### **Power Features Table**

| Operation<br>Voltage | Operation<br>Current (12<br>MHz) | Operation<br>Current (6 MHz) | Operation<br>Current (3 MHz) | Operation<br>Current (1.5 MHz) | Operation<br>Temperature |

|----------------------|----------------------------------|------------------------------|------------------------------|--------------------------------|--------------------------|

| 2.2 ~ 5.5 V          | <b>15 mA</b>                     | <b>7 mA</b>                  | <b>5 mA</b>                  | <b>4 mA</b>                    | -40 to + 85              |

| Battery mode         | (WKT ON)                         | (WKT ON)                     | (WKT ON)                     | (WKT ON)                       |                          |

## **Peripheral Features Table**

| USB<br>control | Interrupt<br>mode | Bulk<br>mode | Touch<br>Key | PWM<br>Output | I80<br>Interface | SPI<br>Interface |

|----------------|-------------------|--------------|--------------|---------------|------------------|------------------|

| EP0 each       | EP1 & EP2         | EP3 & EP4    | Capacitive   | 8-Bit         | Nand-Flash       | Master only      |

| 8-Byte         | 8-Byte            | 64-Byte      | 5-ch         | CPUCLK        | DMA R/W          | DMA R/W          |

## TMU313 series Family Types

| P/N       | Program<br>ROM | RAM<br>bytes | EP | GPIO | PWM | Touch<br>key | CPU<br>Clock   | 180 | SPI<br>Master |

|-----------|----------------|--------------|----|------|-----|--------------|----------------|-----|---------------|

| TMU3130   | 8K*14 Flash    | 160 +128     | 5  | 36   | 1   | 5            | IRC / 6<br>MHz | Yes | Yes           |

| TMU3131   | 6K*14 MTP      | 160 +128     | 5  | 17   | 1   | 5            | IRC            | _   | Yes           |

| TMU3132   | 4K*14 MTP      | 160 +128     | 5  | 16   | _   | _            | IRC            | _   | Yes           |

| TMU3132MS | 4K*14<br>MASK  | 160 +128     | 5  | 16   | _   | _            | IRC            | _   | Yes           |

## Features

#### **RISC CPU:**

- Only 37 instructions

- ♦ Instruction Execution Time

- 2-cycle instructions except branch

- Operating clock

- Fast Clock:

- -External XTAL: 6 MHz

- Internal 48 MHz PLL

- -FIRC (Internal RC 48 MHz +/-3%)

- CPU Clock control:

- $-\,12$  MHz / 6 MHz / 3 MHz / 1.5 MHz

- Clock Output:

- $-\,6$  MHz / 12 MHz Output

- ♦ 8Kx14 internal flash Program Memory

- ♦ Memory

- 160 bytes on F-Plane

- 128 bytes on R-Plane

- 8 bytes \*5 on R-Plane

#### 8-level Stack

- ♦ Interrupt

- 16 kinds of interrupt vector

- USB EP0 SET0 Receive Interrupt

- USB EP0 OUT Receive Interrupt

- USB EP0 Transmit Interrupt

- USB EP1 Transmit Interrupt

- USB EP2 Transmit Interrupt

- USB Suspend Interrupt

- USB EP3 Bulk Transmit Interrupt

- USB EP4 Bulk Transmit Interrupt

- USB Bus Reset Interrupt

- USB Resume Interrupt

- Wake-up Timer Interrupt

- Timer0 Interrupt

- PB0 External I/O Interrupt

- PC[0..7] External Keyboard Interrupt

- VDD5V Rise interrupt

- Timer1 Interrupt

- Automatic Store/Restore W and STATUS

#### **Power Features**

- Operation Voltage

- Low Voltage Reset Voltage to 5.5V

- Maximum Operation range 2.1V to 5.5V Built-in 3.3V Regulator covers 3.3 to 5.5V

- Chip Operating Voltage range 2.1 to 3.6V

#### Operation Current

- USB mode (Internal 3.3V Regulator used) • Normal mode

- -5V@ 12 MHz, 13.9 mA typical

- -5V@ 6 MHz, 6.8 mA typical

- -5V@ 3 MHz, 4.8 mA typical

- -5V@ 1.5 MHz, 3.9 mA typical

- Suspend mode

- -5V@ 12 MHz, 350 uA typical

- Power down mode -5V@ 1 uA typical

- H/W Reset

- External active low reset (RSTN)

- Build-in Power-On Reset (POR)

- Low Voltage Reset 2.1V (LVR)

- Watchdog Reset (WDT)

#### **Peripheral Features**

- ♦ I/O Port:

- Maximum 36 programmable I/O pins

- Pseudo-Open-Drain Output (P.O.D.)

- Open-Drain Output (O.D.)

- CMOS Push-Pull Output (P.P.)

- Schmitt Trigger Input

- ♦ Capacitive Touch Module

- Up to16 channels for Touch Key

- ♦ Timers

- Timer0 is 8-bit with 8-bit prescaler, Counter/Capture/Interrupt function

- Timer1 is 16-bit with Buzzer / Capture / Reload / Interrupt function

#### ♦ PWMs

- Built-in 8-bit PWM generator

- PWM0 with prescaler / period adjustment / buffer-reload / rising-falling output

#### ♦ Watchdog Timer

- Clocked by on-chip oscillator with 4 adjustable Reset/Interrupt time durations (112 ms / 56 ms / 28 ms / 14 ms)

- Wake-up Timer (896 ms / 448 ms / 224 ms / 112 ms)

#### SPI Interface

- Master only

- Programmable transmit bit rate

- Serial clock phase and polarity options

- MSB-first or LSB-first selectable

## **Pin Summary (LQFP-48/SSOP-48)**

| NAME                      | I/O  | тми     | 3130    | Package                             |  |  |  |  |

|---------------------------|------|---------|---------|-------------------------------------|--|--|--|--|

|                           |      | LQFP-48 | SSOP-48 |                                     |  |  |  |  |

| VDD5                      | Р    | 36      | 43      |                                     |  |  |  |  |

| VSS                       | Р    | 42      | 1       |                                     |  |  |  |  |

| PC5VIN                    |      | 38      | 45      |                                     |  |  |  |  |

| VBAT                      | Р    | 37      | 44      |                                     |  |  |  |  |

| V33                       | 0    | 46      | 5       |                                     |  |  |  |  |

| X1                        | I    | 39      | 46      |                                     |  |  |  |  |

| X2                        | 0    | 40      | 47      |                                     |  |  |  |  |

| VPP/RSTn                  | I    | 6       | 13      |                                     |  |  |  |  |

| VSSA                      | Р    | 43      | 2       | 48 47 46 45 44 43 42 41 40 39 38 37 |  |  |  |  |

| VDDA                      | Р    | 45      | 4       |                                     |  |  |  |  |

| FLT                       | 0    | 44      | 3       | □ 2 35 □                            |  |  |  |  |

| PA[7] \ 180 RD            | 1/0  | 24      | 31      | 3 34                                |  |  |  |  |

| PA[6] \ SPI DO            | 1/0  | 33      | 40      |                                     |  |  |  |  |

| PA[5] \ SPI CLK           | 1/0  | 34      | 41      |                                     |  |  |  |  |

| PA[4] \ SPI DI            | 1/0  | 35      | 42      |                                     |  |  |  |  |

| PA[3] \ I80 WR            | 1/0  | 13      | 20      |                                     |  |  |  |  |

| PA[2] \ TK[2]             | 1/0  | 3       | 10      |                                     |  |  |  |  |

| PA[1] \ TK[3]             | 1/0  | 4       | 11      |                                     |  |  |  |  |

| PA[0] \ TK[4]             | 1/0  | 5       | 12      |                                     |  |  |  |  |

| DP \ PB3 \IIC SCK         | 1/0  | 47      | 6       | <b>1</b> 2 25                       |  |  |  |  |

| DM \ PB2 \ IIC DAT        | 1/0  | 48      | 7       | 13 14 15 16 17 18 19 20 21 22 23 24 |  |  |  |  |

| PB[0] \ TK[0]             | 1/0  | 2       | 9       |                                     |  |  |  |  |

| PB[1] \ TK[1]             | 1/0  | 1       | 8       |                                     |  |  |  |  |

| PC[0] \ KSI[0] \ I80_D[0] | 1/0  | 32      | 39      |                                     |  |  |  |  |

| PC[1] \ KSI[1] \ I80_D[1] | 1/0  | 31      | 38      |                                     |  |  |  |  |

| PC[2] \ KSI[2] \ I80_D[2] | 1/0  | 30      | 37      |                                     |  |  |  |  |

| PC[3] \ KSI[3] \ I80_D[3] | 1/0  | 29      | 36      |                                     |  |  |  |  |

| PC[4] \ KSI[4] \ I80_D[4] | 1/0  | 28      | 35      |                                     |  |  |  |  |

| PC[5] \ KSI[5] \ I80_D[5] | 1/0  | 27      | 34      |                                     |  |  |  |  |

| PC[6] \ KSI[6] \ I80 D[6] | 1/0  | 26      | 33      | 5 44                                |  |  |  |  |

| PC[7] \ KSI[7] \ I80_D[7] | 1/0  | 25      | 32      |                                     |  |  |  |  |

| PD[0] \ KSO[0]            | 1/0  | 7       | 14      |                                     |  |  |  |  |

| PD[1] \ KSO[1]            | 1/0  | 8       | 15      | 10 39                               |  |  |  |  |

| PD[2] \ KSO[2]            | 1/0  | 9       | 16      |                                     |  |  |  |  |

| PD[3] \ KSO[3]            | 1/0  | 10      | 17      |                                     |  |  |  |  |

| PD[4] \ KSO[4]            | 1/0  | 11      | 18      | 14 35 1<br>15 34 1                  |  |  |  |  |

| PD[5] \ KSO[5]            | 1/0  | 12      | 19      | 16 33                               |  |  |  |  |

| PD[6] \ KSO[6]            | 1/0  | 14      | 21      |                                     |  |  |  |  |

| PD[7] \ KSO[7]            | 1/0  | 15      | 22      | 19 30 1<br>20 29 1                  |  |  |  |  |

| PE[0] \ KSO[8]            | 1/0  | 16      | 23      | 21 28                               |  |  |  |  |

| PE[1] \ KSO[9]            | 1/0  | 10      | 23      | 22 27 27<br>23 26<br>24 25          |  |  |  |  |

| PE[2] \ KSO[10]           | 1/0  | 18      | 25      | 24 25                               |  |  |  |  |

| PE[3] \ KSO[11]           | 1/0  | 10      | 26      |                                     |  |  |  |  |

| PE[4] \ KSO[12]           | 1/0  | 20      | 20      |                                     |  |  |  |  |

| PE[5] \ KSO[13]           | 1/0  | 20      | 28      |                                     |  |  |  |  |

| PE[6] \ KSO[14]           | 1/0  | 21      | 20      |                                     |  |  |  |  |

|                           | ., 0 |         | 25      |                                     |  |  |  |  |

tenx technology inc.

## **Pin Summary (LQFP-48/SSOP-48)**

| Pi<br>num |         |                    |      | Inj            | put            | (         | Dutpu  | ıt   | set               | А        | lternate  | Functio | 'n  |                 |

|-----------|---------|--------------------|------|----------------|----------------|-----------|--------|------|-------------------|----------|-----------|---------|-----|-----------------|

| LQFP-48   | SSOP-48 | Pin Name           | Type | Enable Pull-up | Ext. Interrupt | 0.D.      | P.O.D. | P.P. | Func. after reset | Keyboard | Touch-Key | I80     | IdS | Misc            |

| 1         | 8       | TK0 / PB1          | I/O  |                |                | •         |        | •    | PB1               |          | •         |         |     |                 |

| 2         | 9       | TK1 / PB0          | I/O  | •              | •              | $\bullet$ |        | •    | PB0               |          | •         |         |     |                 |

| 3         | 10      | TK2 / PA2          | I/O  | •              |                |           | ●      | •    | PA2               |          | •         |         |     |                 |

| 4         | 11      | TK3 / PA1          | I/O  | •              |                |           | •      | •    | PA1               |          | •         |         |     |                 |

| 5         | 12      | TK4 / PA0          | I/O  | •              |                |           | •      | •    | PA0               |          | •         |         |     |                 |

| 6         | 13      | VPP / RSTN         | Ι    |                |                |           |        |      | RSTN              |          |           |         |     | Reset           |

| 7         | 14      | KSO0 / PD0         | I/O  | •              |                |           | •      | •    | PD0               | •        |           |         |     |                 |

| 8         | 15      | KSO1 / PD1         | I/O  | •              |                |           | •      | •    | PD1               | •        |           |         |     |                 |

| 9         | 16      | KSO2 / PD2         | I/O  | •              |                |           | ٠      | •    | PD2               | •        |           |         |     |                 |

| 10        | 17      | KSO3 / PD3         | I/O  | •              |                |           | •      | •    | PD3               | •        |           |         |     |                 |

| 11        | 18      | KSO4 / PD4         | I/O  | •              |                |           | •      | •    | PD4               | •        |           |         |     |                 |

| 12        | 19      | KSO5 / PD5         | I/O  | •              |                |           | •      | •    | PD5               | •        |           |         |     |                 |

| 13        | 20      | I80WR / PA3        | I/O  | •              |                |           | •      | •    | PA3               |          |           | •       |     |                 |

| 14        | 21      | KSO6 / PD6         | I/O  | •              |                |           | ●      | •    | PD6               | •        |           |         |     |                 |

| 15        | 22      | KSO7 / PD7         | I/O  | •              |                |           | ۲      | •    | PD7               | •        |           |         |     |                 |

| 16        | 23      | PWMO / KSO8 / PE0  | I/O  | •              |                |           | ●      | •    | PE0               | •        |           |         |     | PWM<br>Output   |

| 17        | 24      | KSO9 / PE1         | I/O  | •              |                |           | ۲      | •    | PE1               | •        |           |         |     |                 |

| 18        | 25      | KSO10 / PE2        | I/O  | •              |                |           | ●      | •    | PE2               | •        |           |         |     |                 |

| 19        | 26      | CLKO / KSO11 / PE3 | I/O  | •              |                |           | •      | •    | PE3               | •        |           |         |     | Clock<br>Output |

| 20        | 27      | KSO12 / PE4        | I/O  | •              |                |           | •      | •    | PE4               | •        |           |         |     |                 |

| 21        | 28      | KSO13 / PE5        | I/O  | •              |                |           | •      | •    | PE5               | •        |           |         |     |                 |

| 22        | 29      | KSO14 / PE6        | I/O  | •              |                |           | •      | •    | PE6               | •        |           |         |     |                 |

| 23        | 30      | KSO15 / PE7        | I/O  | •              |                |           | •      | •    | PE7               | •        |           |         |     |                 |

| 24        | 31      | I80RD / PA7        | I/O  | •              |                |           | •      | •    | PA7               |          |           | •       |     |                 |

| 25        | 32      | KSI7 / D7 / PC7    | I/O  |                |                | •         |        |      | PC7               | •        |           | •       |     |                 |

| 26        | 33      | KSI6 / D6 / PC6    | I/O  | •              | •              | •         |        | •    | PC6               | •        |           | •       |     |                 |

| 27        | 34      | KSI5 / D5 / PC5    | I/O  | •              | •              | •         |        |      | PC5               | •        |           | •       |     |                 |

| 28        | 35      | KSI4 / D4 / PC4    | I/O  | •              | •              | •         |        | •    | PC4               | •        |           | •       |     |                 |

| 29        | 36      | KSI3 / D3 / PC3    | I/O  | •              | •              | •         |        | •    | PC3               | •        |           | •       |     |                 |

| 30        | 37      | KSI2 / D2 / PC2    | I/O  | •              | •              | •         |        | •    | PC2               | •        |           | •       |     |                 |

## UM-TMU3130\_ED USB Microcontroller

| P:<br>nun |         |                 |      | Inj            | put            | C    | Jutpu  | ıt   | set               | А        | lternate  | Functio | on  |           |

|-----------|---------|-----------------|------|----------------|----------------|------|--------|------|-------------------|----------|-----------|---------|-----|-----------|

| LQFP-48   | SSOP-48 | Pin Name        | Type | Enable Pull-up | Ext. Interrupt | 0.D. | P.O.D. | P.P. | Func. after reset | Keyboard | Touch-Key | I80     | SPI | Misc      |

| 31        | 38      | KSI1 / D1 / PC1 | I/O  | •              | •              | •    |        | •    | PC1               | •        |           | •       |     |           |

| 32        | 39      | KSI0 / D0 / PC0 | I/O  | •              | ●              | ●    |        | ●    | PC0               | •        |           | •       |     |           |

| 33        | 40      | SDO / PA6       | I/O  | •              |                |      | ●      | ●    | PA6               |          |           |         | •   |           |

| 34        | 41      | SCLK / PA5      | I/O  | •              |                |      | ●      | ●    | PA5               |          |           |         | •   |           |

| 35        | 42      | SDI / PA4       | I/O  | •              |                |      | ●      | ●    | PA4               |          |           |         | •   |           |

| 36        | 43      | VDD5            | Р    |                |                |      |        |      | VDD5              |          |           |         |     |           |

| 37        | 44      | VBAT            | Р    |                |                |      |        |      | VBAT              |          |           |         |     |           |

| 38        | 45      | PC5VIN          | Ι    |                |                |      |        |      | PC5VIN            |          |           |         |     |           |

| 39        | 46      | X1              | Ι    |                |                |      |        |      | X1                |          |           |         |     | X'tal-in  |

| 40        | 47      | X2              | 0    |                |                |      |        |      | X2                |          |           |         |     | X'tal-out |

| 41        | 48      | NC              |      |                |                |      |        |      | NC                |          |           |         |     |           |

| 42        | 1       | VSS             | Р    |                |                |      |        |      | VSS               |          |           |         |     |           |

| 43        | 2       | VSSA            | Р    |                |                |      |        |      | VSSA              |          |           |         |     |           |

| 44        | 3       | FLT             | 0    |                |                |      |        |      | FLT               |          |           |         |     | Filter    |

| 45        | 4       | VDDA            | Р    |                |                |      |        |      | VDDA              |          |           |         |     |           |

| 46        | 5       | VDD             | Р    |                |                |      |        |      | VDD               |          |           |         |     |           |

| 47        | 6       | DP / SCK / PB3  | I/O  | •              |                | •    |        | •    | DP                |          |           |         |     | USB       |

| 48        | 7       | DM / DAT / PB2  | I/O  | •              |                | •    |        | •    | DM                |          |           |         |     | USB       |

Symbol: O.D. = Open Drain

P.O.D. = Pseudo Open Drain

P.P. = Push-Pull Output

PS:

- 1. PE[3] can be configured as clock output.

- 2. PE[0] can output PWM by setting Register.

- 3. PB[3..1] and PC[7..0] support Open Drain, and the other use of Pseudo Open Drain

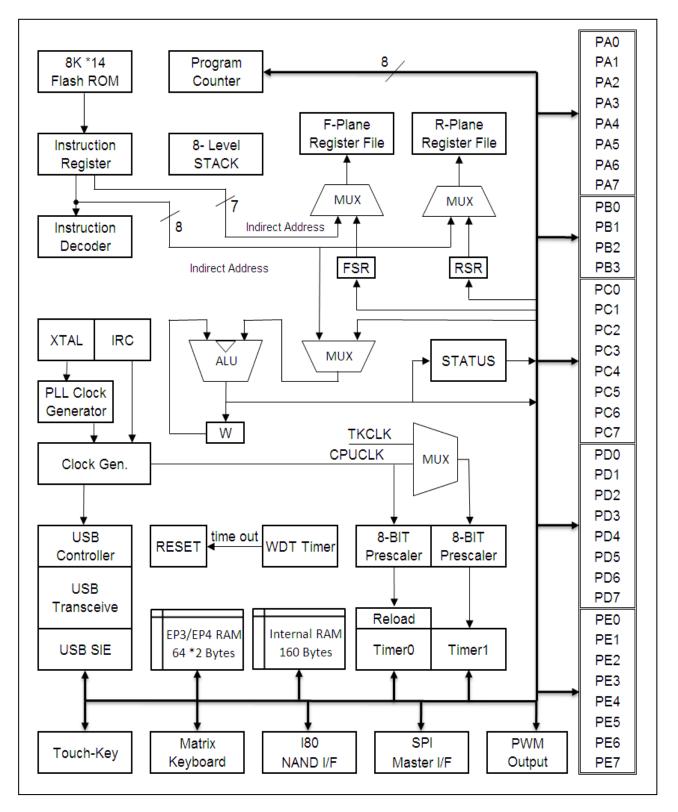

## System Block Diagram

## CONTENTS

| 1. | CPU  | U Core          | Description                                     | 9  |

|----|------|-----------------|-------------------------------------------------|----|

|    | 1.1  | Clock           | Scheme and Instruction Cycle                    | 9  |

|    |      |                 | Vector                                          |    |

|    | 1.3  | Addres          | sing Mode                                       | 11 |

|    | 1.4  | Program         | m Memory                                        | 12 |

|    | 1.5  |                 | Memory                                          |    |

|    | 1.6  | •               | n Configuration Register (SYSCFG)               |    |

|    |      |                 | ower and Battery Power                          |    |

|    |      |                 | p Timer and Watch Dog Timer                     |    |

|    |      |                 | ): 8-bit Timer with Pre-scaler (PSC)            |    |

|    | 1.10 | Timerl          | : 8-bit Timer/Counter with Pre-scale (PSC)      | 18 |

| 2. | Fun  | iction <b>E</b> | Description                                     | 19 |

|    | 2.1  | Interru         | pt Vectors                                      | 19 |

|    |      |                 | Iemory Map (F-Plane)                            |    |

|    |      |                 | Iemory Map (R-Plane)                            |    |

|    |      |                 | m Counter (PC) and Stack                        |    |

|    |      |                 | lock and Clock Control Register                 |    |

|    |      |                 | al Interrupt Input (PB0 and Keyboard Interrupt) |    |

|    | 2.7  |                 | sing Mode                                       |    |

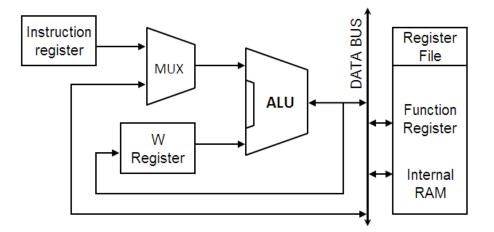

|    | 2.8  |                 | LU and Working (W) Register                     |    |

|    | 2.9  |                 | US Register                                     |    |

| 3. | Peri | ipheral         | Functional Block                                | 34 |

|    |      |                 | nterface                                        |    |

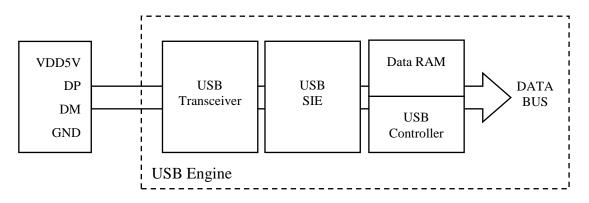

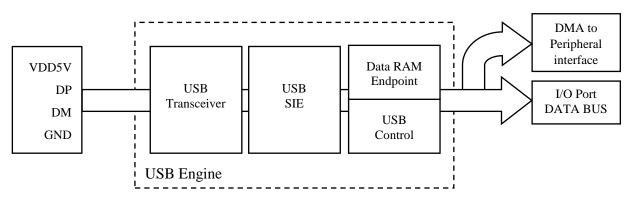

|    |      | 3.1.1           | USB Engine Functional Description               |    |

|    |      | 3.1.2           | USB Control and Status Register Control         |    |

|    |      | 3.1.3           | USB Suspend and Resume                          |    |

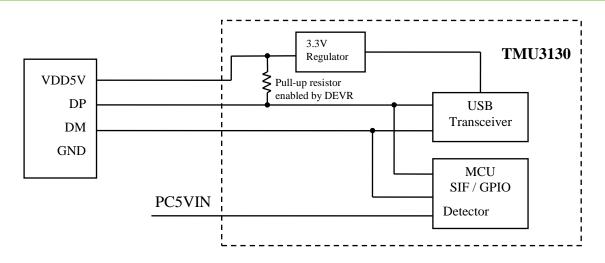

|    |      | 3.1.4           | USB Internal DP Pull-up Resistor                |    |

|    |      | 3.1.5           | USB Device Address                              |    |

|    |      | 3.1.6           | USB Endpoint                                    |    |

|    |      | 3.1.7           | USB Endpoint 0 Receive (SET0/OUT0)              |    |

|    |      |                 | USB Endpoint 0 Transmit (TX0)                   |    |

|    |      | 3.1.9           | USB Endpoint 1/2 Transmit (TX1/2)               |    |

|    |      |                 | USB Endpoint 3/4 Bulk Transfer (TX3/RC4)        |    |

|    |      |                 | USB Endpoint 3 Transmit (TX3)                   |    |

|    |      |                 | USB Endpoint 4 Receive (RC4).                   |    |

|    |      |                 | USB Reset and Power Management                  |    |

|    |      |                 | USB Interrupt Vector                            |    |

|    |      |                 | USB DMA Transfer Mode                           |    |

|    |      |                 | USB Device Initialization                       |    |

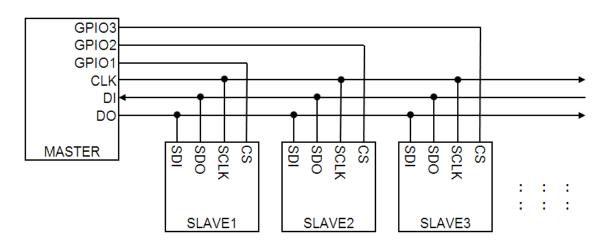

|    | 3.2  |                 | Peripheral Interface (SPI)                      |    |

|    |      | 3.2.1           | SPI Functional Description                      |    |

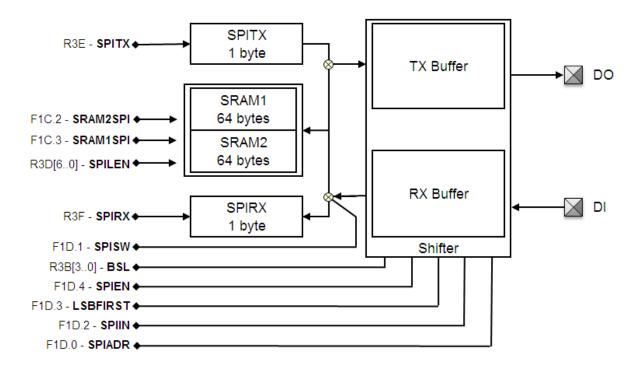

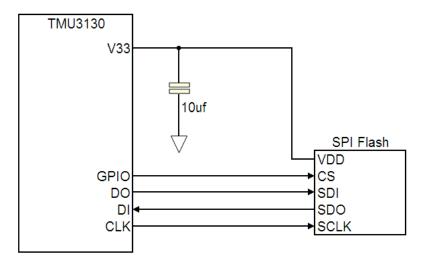

|    |      | 3.2.2           | SPI System Block diagram and Register Control   |    |

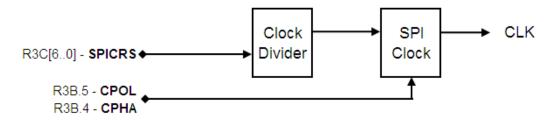

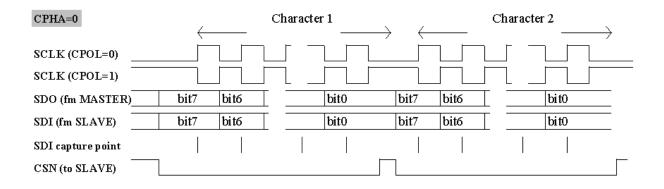

|    |      | 3.2.3           | SPI Clock and Data Format                       |    |

|    |      | 3.2.4           | SPI Power Circuit                               |    |

|    |      |                 |                                                 |    |

| _      |               |                                               |      |

|--------|---------------|-----------------------------------------------|------|

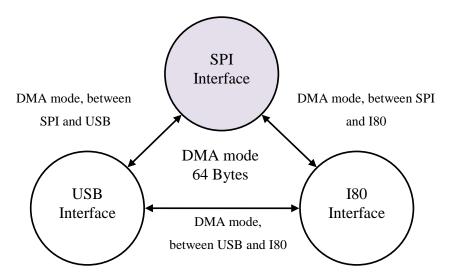

|        | 3.2.5         | SPI DMA Transfer Mode                         | 63   |

|        | 3.2.6         | SPI Initial Sample Code                       |      |

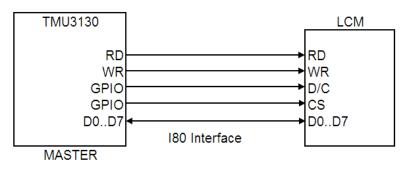

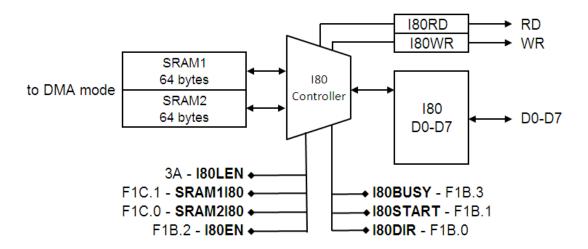

| 3.3    | 180 Pe        | eripheral Interface (I80)                     | 65   |

|        | 3.3.1         | I80 Functional Description                    |      |

|        | 3.3.2         | I80 System Block Diagram and Register Control |      |

|        | 3.3.3         | I80 Clock and Data Format                     |      |

|        | 3.3.4         | I80 DMA Transfer Mode                         | 67   |

|        | 3.3.5         | I80 Initial Sample Code                       | 68   |

| 3.4    | Touch         | 1 Key                                         |      |

|        | 3.4.1         | Touch Key Functional Description              | 69   |

|        | 3.4.2         | Touch Key Block Diagram                       | 70   |

|        | 3.4.3         | Touch Key System Register Control             | 70   |

|        | 3.4.4         | Touch Key Function Flowchart                  |      |

|        | 3.4.5         | Touch Key Initial Sample Code                 | 73   |

| 3.5    | 8-bit I       | PWM Output                                    | 74   |

|        | 3.5.1         | PWM Functional Description                    | 74   |

|        | 3.5.2         | PWM System Block Diagram and Register Control | 74   |

|        | 3.5.3         | PWM Clock and Duty Output                     | 75   |

|        | 3.5.4         | PWM Initial Sample Code                       | 76   |

| 3.6    | Syster        | n Clock Oscillator                            |      |

|        | 3.6.1         | Clock Block Diagram and Symbol                |      |

|        | 3.6.2         | System Clock Register Control                 | 77   |

|        | 3.6.3         | External Oscillator Description               |      |

|        | 3.6.4         | Internal RC Description                       |      |

| 3.7    |               | ort Description                               |      |

|        | 3.7.1         | Port A [70]                                   |      |

|        | 3.7.2         | Port B [30]                                   |      |

|        | 3.7.3         | Port C [70]                                   |      |

|        | 3.7.4         | Port D [70]                                   |      |

|        | 3.7.5         | Port E [70]                                   | 87   |

| 4. Sys | stem Co       | ontrol Registers                              | 90   |

| 4.1    | F-Plan        | e Register Table                              | 90   |

| 4.2    | F-Plan        | e Register Description                        | 91   |

|        |               | ne Register Table                             |      |

|        |               | ne Register Description                       |      |

| 5. Ins | tructio       | n Set                                         | .122 |

| 5.1    | Explai        | nation of symbols                             | .122 |

|        |               | ction Set Table                               |      |

|        |               | ction Set Description                         |      |

|        |               | Characteristics                               |      |

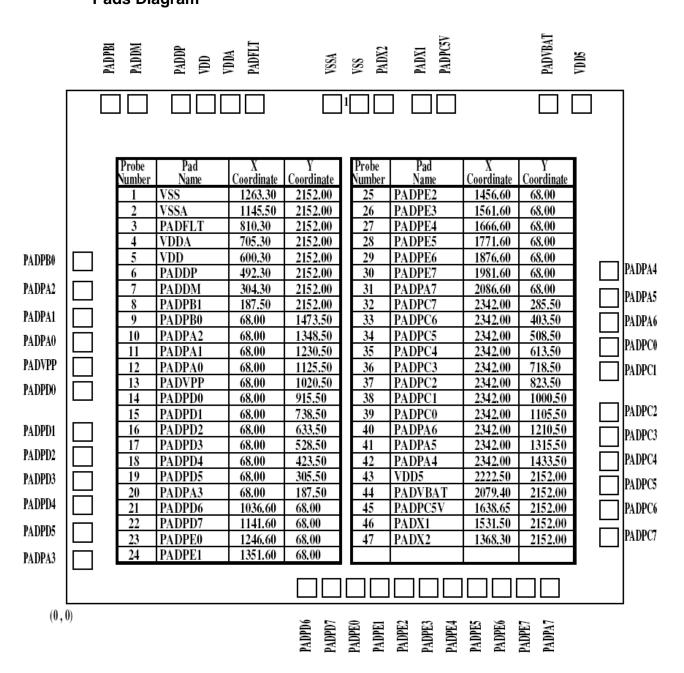

|        |               | nd Dice Information                           |      |

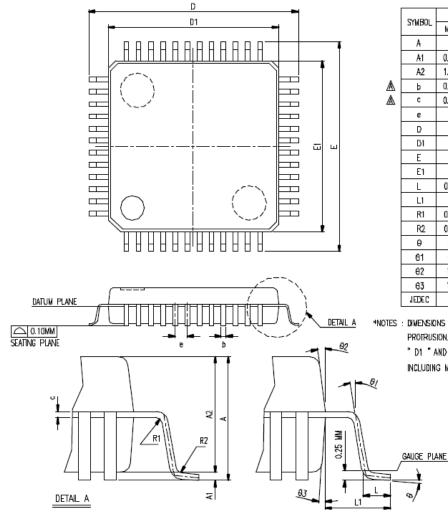

| LO     | FP-48 P       | ackage Dimension                              | 138  |

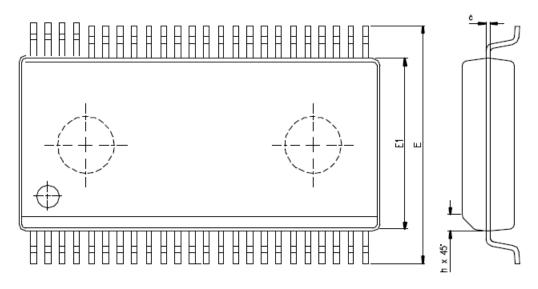

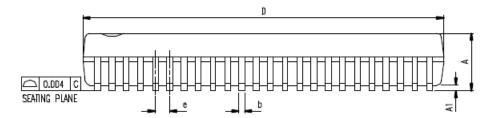

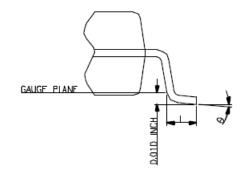

| -      |               | ackage Dimension                              |      |

|        |               | am                                            |      |

|        | $\mathcal{O}$ |                                               |      |

## 1. CPU Core Description

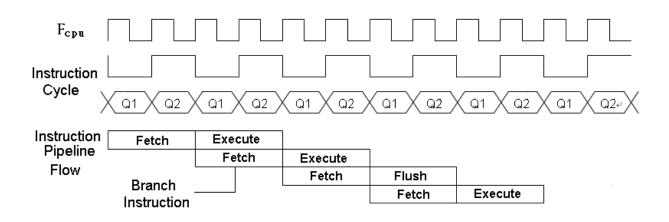

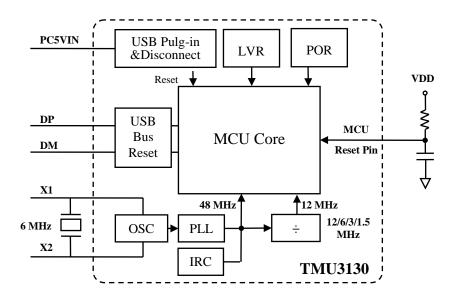

#### 1.1 Clock Scheme and Instruction Cycle

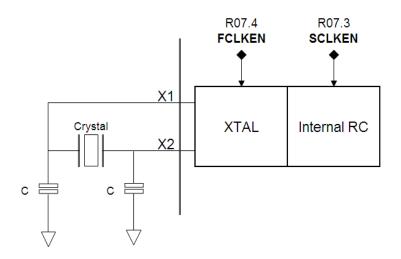

TMU3130 has 2 chip clock sources as following:

$F_{xtal_{6m}}$  : External 6 MHz Crystal Oscillator clock

F<sub>re</sub> : Internal RC oscillator 24 MHz clock

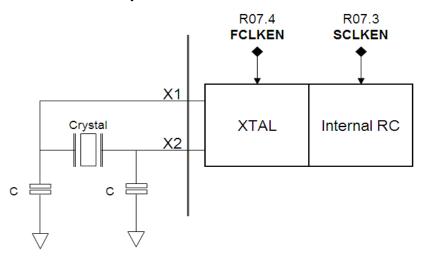

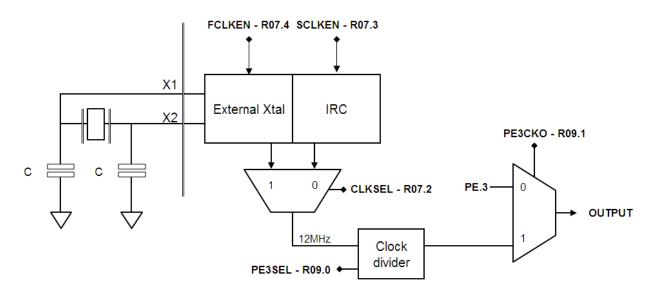

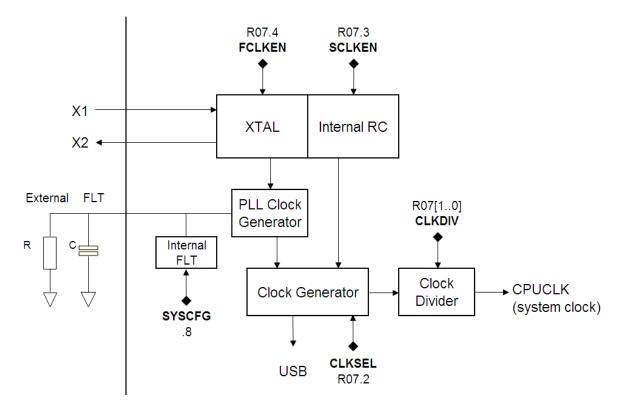

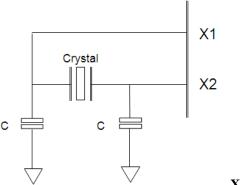

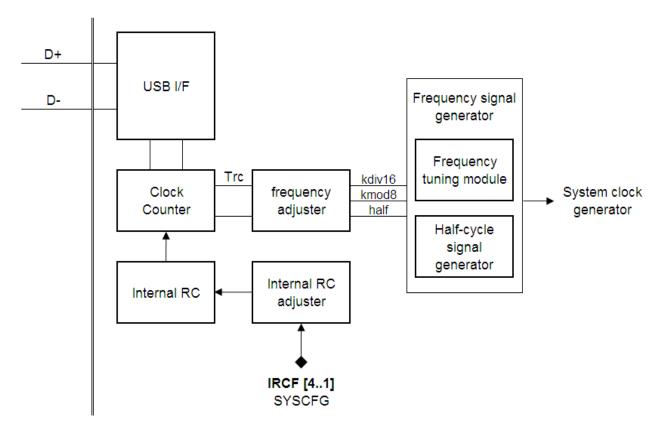

$F_{xtal_6m}$  is popup to 48 MHz clock ( $F_{pll}$ ) by PLL. The  $F_{pll}$  clock will be used for USB and for CPU clock.  $F_{rc}$  can be synchronized by USB signals and popup to 48 MHz clock for USB module.  $F_{rc}$  can also be used for CPU clock. Clock Control register FCLKEN (FCLKEN - R07.4) SCLKEN (SCLKEN – R07.3h) is used to enable external 6 MHz crystal oscillator or internal oscillator.

The system clock (Fcpu) is internally divided by two to generate Q1 state and Q2 state for each instruction cycle. The Programming Counter (PC) is updated at Q1 and the instruction is fetched from program ROM and latched into the instruction register in Q2. It is then decoded and executed during the following Q1-Q2 cycle. The Branch instructions take 2 cycles which is always related to the current program counter. That is, the next instruction is obtained by adding a signed offset to current program counter.

#### **1.2 Reset Vector**

The TMU3130 can be RESET in four ways:

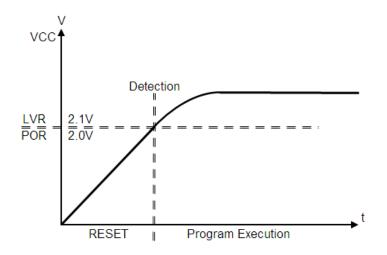

- Power-On-Reset (POR)

- Low Voltage Reset (LVR)

- External Pin Reset (RSTN)

- Watchdog Reset (WDT)

Power-On-Reset (**POR**): After Power-On-Reset, all system and peripheral control registers are then set to their default hardware Reset values. The Internal Filter or External Filter is selected by the SYSCFG register value.

Low Voltage Reset (LVR): The Low Voltage Reset features static reset when supply voltage is below a threshold level. Generally, the LVR of TMU31 series provides 2.1 voltages to meet the needs of product designs.

| HOST | VCC   |              |

|------|-------|--------------|

| GPIO | Reset | RSTN         |

| OPIO |       | Koth         |

| MCU  | GND   | TMU31 series |

External Pin Reset (**RSTN**): The External reset inputs are held high via Pull up resistors while the threshold input is simply grounded. Thus configured, pulling the trigger momentarily to ground acts as a 'set' and transitions the output pin to high state.

WatchDog Reset (**WDT**): The watchdog timer is a computer hardware that triggers a system reset or other corrective action if some fault conditions occur in the main program. This function is to bring the system back from the unresponsive state into normal operation. These two resets also set all the control registers to their default reset value.

#### 1.3 Addressing Mode

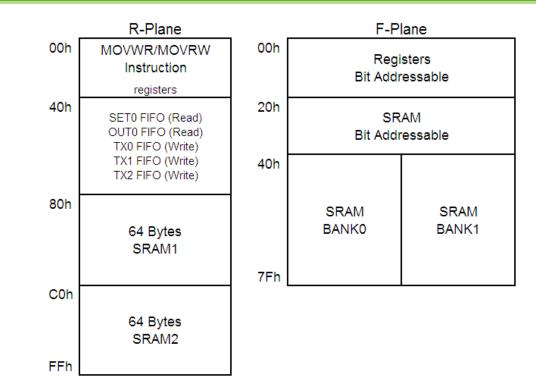

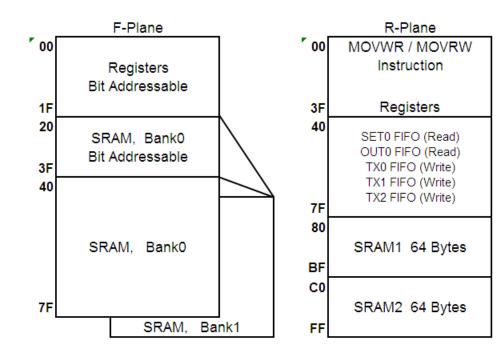

There are two Data Memory Planes in CPU, i.e. R-Plane and F-Plane. The lower locations of F-Plane are reserved for the SFR. Above the SFR is General Purpose Data Memory, which is implemented as static RAM. F-Plane can be addressed directly or indirectly. Indirect Addressing is done by INDF register. The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a pointer). The first half of F-Plane is bit-addressable, while the second half of F-Plane is not bit-addressable. R-plane can be accessed indirectly via RSR register.

• 8K x 14 program FLASH.

- 160-byte SRAM (F-Plane) is addressed from 0x20 to 0x7F which is used for CPU. The lower 32-byte (0x20 ~ 0x3f) is bit addressable. The higher address (0x40 ~ 0x7F) is separated to two banks which can be selected by register RAMBANK (RAMBANK F03.5h).

- Two 64-byte RAMs and five 8-byte USB FIFOs are allocated in R-Plane.

The F-Plane supports various instructions operation, such as ADDWF, INCF, MOVWF, etc ...; while the R-Plane only supports MOVWR and MOVRW instructions to exchange data between R-Plane and W-Register.

The lower locations of R-Plane are reserved for read or write registers. Above the registers are the USB FIFO, XRAM Endpoint and static RAM. R-Plane can be accessed indirectly via RSR (F05h) register and INDR (R00h). The INDR register is not a physical register. Addressing INDR actually addresses the register whose address is contained in the RSR register.

The lower locations of F-Plane are reserved for the SFR. Above the SFR is General Purpose Data Memory, which is implemented as static RAM. F-Plane can be addressed directly or indirectly. Indirect addressing the register which address is contained in the FSR register. The first half of F-Plane is bit-addressable (20h~3Fh), while the second half of F-Plane is not bit-addressable (40h~7Fh).

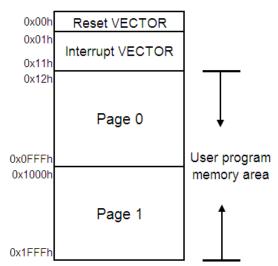

#### 1.4 Program Memory

The Program Memory of this device is 8K \*14 words Flash ROM. It includes Reset vector, Interrupt vector, General purpose program area and additional Manufacture Reserved area. The Reset vector is the beginning address of program. When system is powered on or External reset pin is active low or power support is under LVR reference voltage, the program counter will start on Address 0x0000h. The Interrupt vector is the head of interrupt service routine when any interrupt occurs. The General purpose program area is main program area including main program loop, program subroutines and data table.

| -     |                                 |

|-------|---------------------------------|

| 0000h | Reset Vector                    |

| 0001h | USB EP0 SET0 Receive Interrupt  |

| 0002h | USB EP0 OUT Receive Interrupt   |

| 0003h | USB EP0 Transmit Interrupt      |

| 0004h | USB EP1 Transmit Interrupt      |

| 0005h | USB EP2 Transmit Interrupt      |

| 0006h | USB Suspend Interrupt           |

| 0007h | USB EP3 Bulk Transmit Interrupt |

| 0008h | USB EP4 Bulk Transmit Interrupt |

| 0009h | USB BUS Reset Interrup          |

| 000Ah | USB Resume Interrup             |

| 000Bh | Wakeup Timer Interrupt          |

| 000Ch | Timer0 Interrupt                |

| 000Dh | PB0 External I/O Interrupt      |

| 000Eh | Key Board Interrupt             |

| 000Fh | VDD5 Rise Interrupt             |

| 0010h | Reserved                        |

| 0011h | Timer1 Interrupt                |

|       | General Purpose<br>Program Area |

| 1FFFh |                                 |

#### Program Memory

TMU3130 supports several interrupts generated by USB Engine, such as EP0 SET0 Receive Interrupt, EP0 OUT Receive Interrupt, EP0 Transmit Interrupt, EP1 Transmit Interrupt, EP2 Transmit Interrupt, EP3 Bulk Transmit Interrupt, EP4 Bulk Transmit Interrupt, USB Suspend Interrupt, USB Bus Reset Interrupt, and USB Resume Interrupt. The other interrupt includes Timer0 Interrupt, Timer1 Interrupt, Wakeup timer Interrupt, PB0 external I/O interrupt, matrix Keyboard Interrupt and VDD5V rise interrupt. Each interrupt sources has its own enable/disable control register bit.

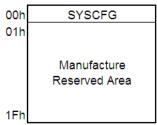

#### 1.5 Config Memory

The Config Memory of TMU3130 is 32 words, which includes System Configuration Register (SYSCFG) and Manufacture Reserved Area. The System Configuration Register (SYSCFG) is located at Flash INFO area. The SYSCFG determines the option for initial condition of MCU. It is written by FLASH Writer only.

The FLASH ROM can be written multi-times and can be read as long as the PROTECT bit of SYSCFG is not set. The SYSCFG can be read no matter PROTECT is set or cleared, but can be written only when PROTECT is not set or FLASH ROM is blank. That is, unprotect the PROTECT bit can be done only if the Program ROM area is blank. The tenx certified writer can do above actions with the sophisticated software.

#### **Config Memory**

#### 1.6 System Configuration Register (SYSCFG)

The System Configuration Register is located at Flash INFO area. The SYSCFG determines the option for initial condition of MCU. It is written by FLASH Writer only. The 13th bit of SYSCFG is code protection selection bit. If this bit is 1, the data in FLASH ROM will be protected, when user reads FLASH ROM.

| Bit  | Name    | Descri | ption                        |

|------|---------|--------|------------------------------|

| 13   | PROTECT | 1      | Code protection              |

| 15   | PROTECT | 0      | No protect                   |

| 12~9 |         | 0      | Reserved                     |

| 8    |         | 0      | External Filter              |

| 0    | Filter  | 1      | Internal Filter              |

| 7~5  |         | 0      | Reserved                     |

| 4~0  | IRCF    | FIRC   | frequency adjustment control |

#### SYSCFG Register table

The TMU3130 supports Internal and External filter for the PLL. The bandwidth of a PLL is the measure of the PLL's ability to track the input clock and jitter. A bandwidth PLL provides a fast lock time and tracks jitter on the reference clock source, passing it through to the PLL output. User can select Internal Filter or External Filter by SYSCFG register. The 13th bit of SYSCFG is code protection selection bit. If this bit is 1, the data in FLASH ROM will be protected when user reads FLASH ROM.

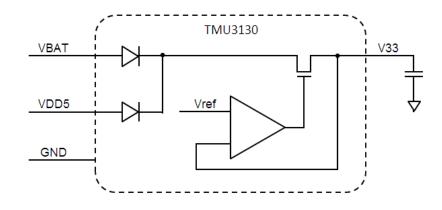

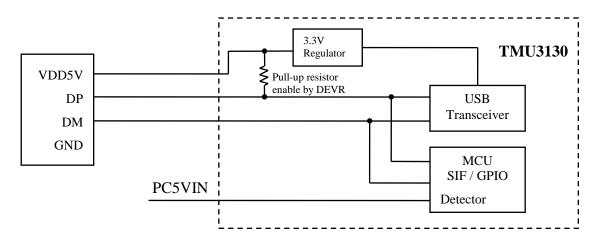

#### **1.7 USB Power and Battery Power**

TMU3130 supports power direct circuit, when USB is plugged-in, it will release battery power automatically to the USB bus power, when USB is unplugged, it will be switched to battery power. Whether plug-in or unplug USB, MCU system will be reset, but the SRAM buffer of TMU3130 will keep the data. On power direct circuit, it has 3.3V voltage regulator output which can be supplied to MCU and peripheral device. The V33 output pin can be supplied up to 60 mA current, output ranges from 3.2V to 3.4V.

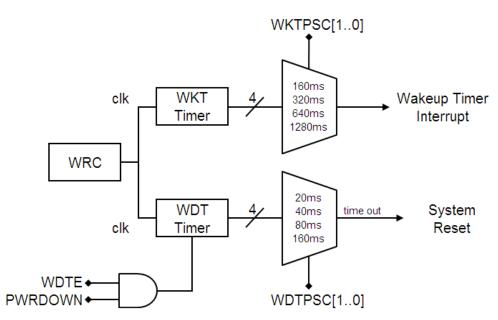

#### 1.8 Wakeup Timer and Watch Dog Timer

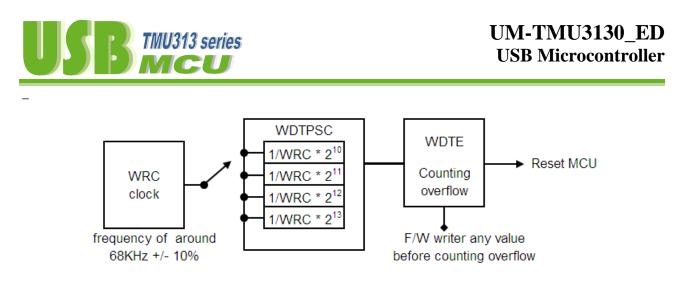

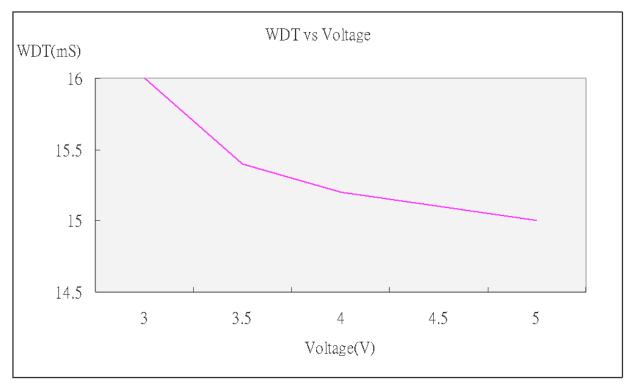

The WKT and WDT use the same internal RC (WRC). This internal RC (WRC) can be disabled by setting **WRCPD - R06.7** "High" for power saving. The overflow period of WDT can be selected from 20 ms to 160 ms and the wakeup period of WKT can be selected from 160 ms to 1280 ms. The WDT is enabled and cleared by the CLRWDT instruction. Once the WDT is enabled, the WDT generates the chip reset signal when WDT overflows. The WKT generates overflow time out interrupt if the corresponding WKT interrupt enable bit is set "High". The WKT works in both Normal mode and Power Down mode. WDT does not work in Power Down mode, it is only designed to prevent F/W goes into endless loops.

The Watch dog timer (WDT) and Wake up timer (WKT) share the same clock source (WRC) which is clocked by on-chip oscillator.

The overflow period of **WDTPSC[1..0]** can be selected from 20 ms, 40 ms, 80 ms and 160 ms. The WDT is cleared by the CLRWDT instruction. If the Watchdog Reset (WDT) is enabled (WDTE=1), then it cannot be stopped, must clear WDTE in selected time (WDTPSC[1..0]), otherwise the WDT generates the chip reset signal to reset MCU system.

The overflow period of WKTPSC[1..0] can be selected from 160 ms, 320 ms, 640 ms and 1280 ms. If the Wake up timer interrupt enable bit (WKTIE) is enabled (WKTIE=1), the WKT will only generates overflow time out signal to interrupt MCU system.

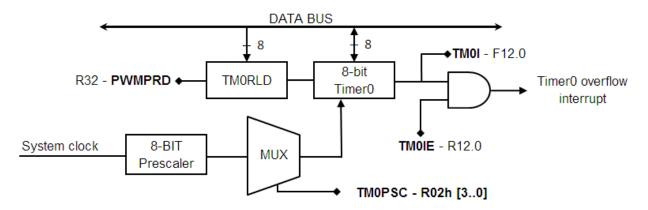

#### **1.9** Timer0: 8-bit Timer with Pre-scaler (PSC)

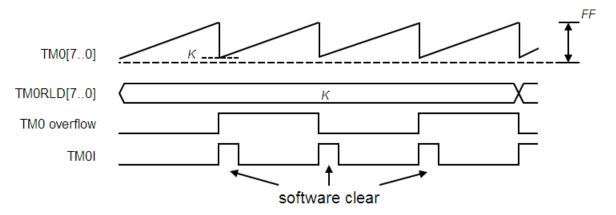

The TMU3130's Timer0 is an 8-bit wide register of **TM0 - F01h**; it can be read or written as any value to register of F-Plane. Besides, Timer0 increases itself periodically and automatically reloads a new "offset value" (**TM0RLD**) while it rolls over based on the pre-scaled instruction clock. The Timer0 increase rate is determined by "Timer0 Pre-Scale" (**TM0PSC**) register in R-Plane. The Timer0 generates overflow time out signal to interrupt MCU system. If the Timer0 interrupt enable bit is enabled, i.e. TM0IE is set to 1 (**TM0IE – R12.0**), the Timer0 can generate interrupt (**TM0I – F12.0**).

The Timer0 is an 8-bit wide register of TIMER0 - F01h. The Timer0 increases itself periodically and rolls over based on the pre-scaled clock source, which can be instruction cycle, the TouchKey oscillating clock rising/falling. The Timer0 increasing rate is determined by "Timer0 Prescale" (TM0PSC) which is registered in R02h[3..0]. The Timer0 will generate interrupt when it counts to overflow if Timer0 interrupt Enable (TM0IE) is set.

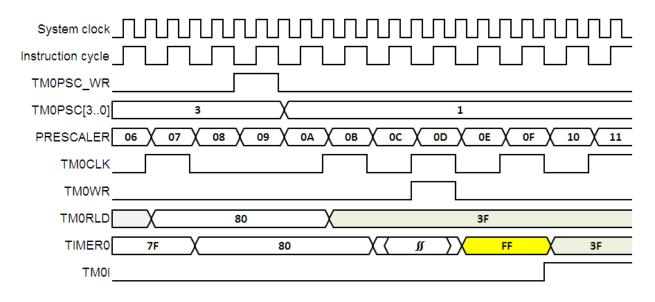

Above figure shows the Timer0 works in pure timer mode. The Timer0 increase rate is determined by "Timer0 Pre-Scale" (**TM0PSC - R02h[3.0]**) which is registered in R-Plane, while it rolls over based on the pre-scaled instruction clock. When the Timer0 prescaler (TM0PSC) is written, the internal 8-bit prescaler will be cleared to 0 to make the counting period correct at the first Timer0 count. The TIMER0 clock source is given only by system clock, goes through the internal 8-bit prescaler, giving to the 8-bit Timer.

Besides, Timer0 increases itself periodically and automatically reloads a new "offset value" (TM0RLD) and the Timer0 generates overflow time out signal to interrupt MCU system. If the Timer0 interrupt enable bit is enabled (**TM0IE**=1), the Timer0 can generate interrupt (TM0I). When Timer0 counts from FFh to 00h, TM0IF (Timer0 Interrupt Flag) will be set to 1 and generate interrupt if **TM0IE** (Timer0 Interrupt Enable) is set.

| TM0PSC.3 | TM0PSC.2 | TM0PSC.1 | TM0PSC.0 | Description                             |  |  |  |

|----------|----------|----------|----------|-----------------------------------------|--|--|--|

| 0        | 0        | 0        | 0        | CLK/1, System clock is divided by 1     |  |  |  |

| 0        | 0        | 0        | 1        | CLK/2, System clock is divided by 2     |  |  |  |

| 0        | 0        | 1        | 0        | CLK/4, System clock is divided by 4     |  |  |  |

| 0        | 0        | 1        | 1        | CLK/8, System clock is divided by 8     |  |  |  |

| 0        | 1        | 0        | 0        | CLK/16, System clock is divided by 16   |  |  |  |

| 0        | 1        | 0        | 1        | CLK/32, System clock is divided by 32   |  |  |  |

| 0        | 1        | 1        | 0        | CLK/64, System clock is divided by 64   |  |  |  |

| 0        | 1        | 1        | 1        | CLK/128, System clock is divided by 128 |  |  |  |

| 1        | 0        | 0        | 0        | CLK/256, System clock is divided by 256 |  |  |  |

TM0PSC[3..0] – Programmable Timer0 Prescaler from System clock

The timing diagram below describes the Timer0 works in counter mode. The instruction cycle consists of 2 system clocks; the system clock signal is synchronized by instruction cycle, which means the high/low time durations of Timer0 clock must be longer than one instruction cycle time to guarantee each Timer0 clock change will be detected correctly by the synchronizer.

Above figure shows that when the Timer0 prescaler (**TM0PSC[3..0]**) is written on Point A, the internal 8-bit prescaler will be cleared to write "1" to make the counting period correct at the first Timer0 count and Timer0 clock will be changed on Point B. When the Timer0 automatically reloads **TM0RLD** written value "3F" on Point C, the Timer0 cannot be changed at this cycle, it has to wait for Timer0 counting to value "FF", and then the TM0WR automatically reloads value "3F" to TM0RLD.

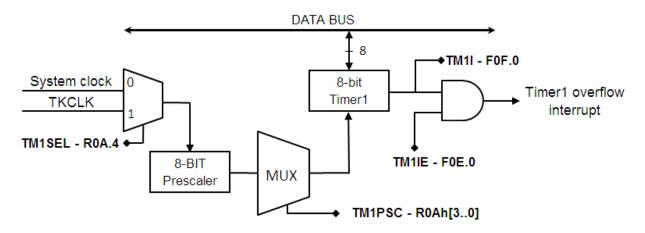

#### **1.10** Timer1: 8-bit Timer/Counter with Pre-scale (PSC)

The TMU3130's Timer1 is an 8-bit wide register (**TM1 - F0Dh**), which can be read or written as any value for register in F-Plane. Besides, Timer1 increases itself periodically and automatically rolls over based on the pre-scaled clock source, which can be the instruction cycle or touch key induced clock (TKCLK). The Timer1 increase rate is determined by "Timer1 Pre-Scale" (**TM1PSC – R0A[3.0]**) register in R-Plane. The Timer1 can generate interrupt (**TM11 – F0F.0**) when it rolls over.

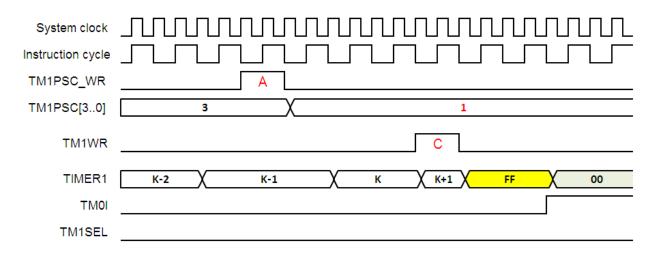

When Timer1 works in pure timer mode, the Timer1 prescaler (TM1PSC – R0A[3..0]) is written, the internal 8-bit prescaler will be cleared to 0 to make the counting period correct at the first Timer1 count. TM1WR is the internal signal that indicates the Timer1 is directly written by instruction; meanwhile, the internal 8-bit prescaler will be cleared. When Timer1 counts from FFh to 00h, Timer1 Interrupt Flag (TM1I – F0F.0) will be set to 1 and generate interrupt if Timer1 Interrupt Enable (TM1IE - F0E.0) is set.

The following timing diagram describes the Timer1 works in counter mode. If TM1SEL=1 (TM1SEL – R0A.4), then the Timer1 counter source clock is from Touch Key module that depends on TKE bit (TKE – R0E.6). In this mode, the counter is used for Touch Key function.

## 2. Function Description

#### 2.1 Interrupt Vectors

The TMU3130 has 1 level, 17 vectors and 24 interrupt sources.

- ➤ USB Endpoint 0 SET0 Receive Interrupt (0001h)

- ➤ USB Endpoint 0 OUT Receive Interrupt (0002h)

- ➤ USB Endpoint 0 Transmit Interrupt (0003h)

- USB Endpoint 1 Transmit Interrupt (0004h)

- USB Endpoint 2 Transmit Interrupt (0005h)

- ➢ USB Suspend Interrupt (0006h)

- USB Endpoint 3 Bulk Transmit Interrupt (0007h)

- USB Endpoint 4 Bulk Transmit Interrupt (0008h)

- ➢ USB Bus Reset Interrupt (0009h)

- ➢ USB Resume Interrupt (000Ah)

- ➢ Wakeup Timer Interrupt (000Bh)

- ➤ Timer0 Interrupt (000Ch)

- ➢ PB0 External I/O Interrupt (000Dh)

- ≻ Keyboard Interrupt (000Eh)

- ➢ VDD5V Rise Interrupt (000Fh)

- ≻ Timer1 Interrupt (0011h)

Each interrupt source has its own enable control bit. An interrupt event will set its individual interrupt flag, no matter its interrupt enable control bit is 0 or 1. Because TMU3130 has 17 vectors, there is an interrupt priority register. Priority of each interrupt is different from each other and the device does not support nested interrupt. Another interrupt can be executed only if the current interrupt is exited (that is, RETI instruction is executed).

## UM-TMU3130\_ED USB Microcontroller

| ;**** I   | NEW ADDR ****  | org 0000h                                | ;Reset Vector     |

|-----------|----------------|------------------------------------------|-------------------|

| goto      | Start          | ·                                        |                   |

| ,         | NEW ADDR ****  | org 0001h                                | ;Interrupt Vector |

| ,<br>goto | EPOSETO        | ; USB Endpoint 0 SET0 Receive Interrupt  |                   |

| goto      | <b>EP0OUT</b>  | ; USB Endpoint 0 OUT Receive Interrupt   |                   |

| goto      | <b>EP0Task</b> | ; USB Endpoint 0 Transmit Interrupt      |                   |

| goto      | EP1Task        | ; USB Endpoint 1 Transmit Interrupt      |                   |

| goto      | EP2Task        | ; USB Endpoint 2 Transmit Interrupt      |                   |

| goto      | SUSPINT        | ; USB Suspend Interrupt                  |                   |

| goto      | EP3Task        | ; USB Endpoint 3 Bulk Transmit Interrupt |                   |

| goto      | EP4Task        | ; USB Endpoint 4 Bulk Transmit Interrupt |                   |

| goto      | USBRST         | ; USB Bus Reset Interrupt                |                   |

| goto      | RUSUINT        | ; USB Resume Interrupt                   |                   |

| goto      | WAKEINT        | ; Wakeup Timer Interrupt                 |                   |

| goto      | TIMEROINT      | ; Timer0 Interrupt                       |                   |

| goto      | PB0INT         | ; PB0 External I/O Interrupt             |                   |

| goto      | KBINT          | ; Keyboard Interrupt                     |                   |

| goto      | VDD5V          | ; VDD5V Rise Interrupt                   |                   |

| goto      | TIMER1INT      | ; Timer1 Interrupt                       |                   |

| <b>a</b>  | :              |                                          |                   |

| Start:    |                |                                          |                   |

| •         |                |                                          |                   |

| END       |                |                                          |                   |

Although the interrupts do not have priority, however, when exit from current interrupt, if there are more than 2 interrupts happen, the priority of the interrupt is:

| Priority | Address     | Source           | Description                        |  |  |  |  |

|----------|-------------|------------------|------------------------------------|--|--|--|--|

| 1        | 01h         | EP0SET0          | Endpoint 0 SET0 Receive Interrupt  |  |  |  |  |

| 2        | 02h         | <b>EP0OUT</b>    | Endpoint 0 OUT Receive Interrupt   |  |  |  |  |

| 3        | 03h         | <b>EP0Task</b>   | Endpoint 0 Transmit Interrupt      |  |  |  |  |

| 4        | 04h         | EP1Task          | Endpoint 1 Transmit Interrupt      |  |  |  |  |

| 5        | 05h         | EP2Task          | Endpoint 2 Transmit Interrupt      |  |  |  |  |

| 6        | 06h         | SUSPINT          | Suspend Interrupt                  |  |  |  |  |

| 7        | 07h         | EP3Task          | Endpoint 3 Bulk Transmit Interrupt |  |  |  |  |

| 8        | 08h         | EP4Task          | Endpoint 4 Bulk Transmit Interrupt |  |  |  |  |

| 9        | 09h         | USBRST           | Bus Reset Interrupt                |  |  |  |  |

| 10       | 0ah         | RUSUINT          | Resume Interrupt                   |  |  |  |  |

| 11       | 0bh         | WAKEINT          | Wakeup Timer Interrupt             |  |  |  |  |

| 12       | 0ch         | <b>TIMER0INT</b> | Timer0 Interrupt                   |  |  |  |  |

| 13       | 0dh         | PB0INT           | PB0 External I/O Interrupt         |  |  |  |  |

| 14       | 0eh         | KBINT            | Key Board Interrupt                |  |  |  |  |

| 15       | 0fh         | VDD5V            | VDD5 Rise Interrupt                |  |  |  |  |

| 16       | 11h         | TIMER1INT        | Timer1 Interrupt                   |  |  |  |  |

| Note     | All Interru | ipt support wak  | eup function                       |  |  |  |  |

#### **Interrupt Priority table 1.5.2:**

If the corresponding interrupt enable bit has been set (INT enable), it will trigger CPU to service the interrupt. CPU accepts interrupt in the end of current executed instruction cycle. In the mean while, a "CALL 00n" (n ranges from 1 to 16) instruction is inserted to CPU, and flag is set to prevent recursive interrupt nesting. The flag is cleared in the instruction after the "RETI" instruction. That is, at least one instruction in main program is executed before service the pending interrupt. The interrupt event is level triggered. F/W must clear the interrupt event register while serving the interrupt routine.

| ,               |          | <br>DDR **** |                                           |              |                        |  |  |  |

|-----------------|----------|--------------|-------------------------------------------|--------------|------------------------|--|--|--|

| ·               | NE VV AI |              | org<br>==========                         | 0001h        | ;Interrupt Vector      |  |  |  |

| ,               | goto     |              | ; Timer0 Interr                           |              |                        |  |  |  |

|                 | •        |              |                                           |              |                        |  |  |  |

| ;====<br>;Funct | ion:Tim  | er0Task      |                                           |              |                        |  |  |  |

| ;====<br>Timer  | )Task:   |              | ; Auto save W                             | and STATUS r |                        |  |  |  |

|                 | reti     |              | ; Auto reload W and STATUS register value |              |                        |  |  |  |

| Start:          |          |              |                                           |              |                        |  |  |  |

|                 | movlw    | HWAUTO       | ; Enable auto s<br>; when interrup        |              | ATUS register function |  |  |  |

|                 | movw     | r CLKCTRL    | , when interrup                           | n occurs     |                        |  |  |  |

|                 | END      |              | ; End of user p                           |              |                        |  |  |  |

The W and STATUS register can be automatically stored into the internal memory when interrupt happens and recalled when exits from interrupt. This functionality is optional and can be enabled or disabled via HWAUTO.

#### **R07h**

| Address | Name   | R/W | Rst | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|--------|-----|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x07    | CLKSEL | W   | 0   |       |       | 0     | 1     | 1     | 0     | 0     | 0     |

#### Bit Name

| Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   |

|-------|-------|--------|--------|--------|--------|---------|---------|

|       |       | W      | W      | W      | W      | W       | W       |

|       |       | HWAUTO | FCLKEN | SCLKEN | CLKSEL | CLKDIV1 | CLKDIV0 |

**R07.5** HWAUTO – Auto push/pop W and STATUS in interrupt subroutine

0: disable

1: enable auto push/pop function

The **HWAUTO** is a setting register bit. The TMU3130 supports H/W auto push/pop W and STATUS function in interrupt subroutine.

| •         | **** NEW AD               | DR ****           | org                                       | /ector             |                  |      |

|-----------|---------------------------|-------------------|-------------------------------------------|--------------------|------------------|------|

| ,         |                           |                   |                                           | 0001h<br>========= | · •              |      |

| 001h      | goto                      | <b>EP0SET0SUB</b> | ; EP0SET Interrup<br>; service routine ad | -                  | -                |      |

|           | •                         |                   |                                           |                    |                  |      |

| ;         | ;======<br>;Function:Time | r0Task            |                                           |                    |                  |      |

| )020h   ] | ;========<br>EP0SET0SUB:  |                   | ; Auto save W and                         |                    |                  |      |

|           | movlw                     | 7fH               | ; 0111.1111b only                         | one bit is cle     | ared, keep other | bits |

|           | movwf                     | INTFLAG1          | ; Clear INTFLAG                           | 1/SET00I into      | errupt register  |      |

|           | reti                      |                   | ; Auto reload W a                         | nd STATUS          | register value   |      |

| 100h S    | Start:                    |                   |                                           |                    |                  |      |

|           | •                         |                   |                                           |                    |                  |      |

|           |                           |                   |                                           |                    |                  |      |

Note that MOVWF instruction must be used to clear the interrupt flag. It is not allowed to use the BCF instruction to clear the F-Plane 0x11h (INTFLAG1) and 0x12h (INTFLAG2) interrupt flag. In TMU310 series and TMU313 series products, if BCF is used to clear the interrupt flag when other interrupt occurs in a new request, then the new request will be lost. Therefore, avoid using the BCF instruction to clear interrupt flag, especially more than 1 or 2 of the interrupt request **at the same time**.

## **2.2 Data Memory Map (F-Plane)**

| Addr       | RST       | NAME     | Bit 7           | Bit 6                                                                       | Bit 5             | Bit 4        | Bit 3        | Bit 2    | Bit 1    | Bit 0    |  |

|------------|-----------|----------|-----------------|-----------------------------------------------------------------------------|-------------------|--------------|--------------|----------|----------|----------|--|

| 00h        | XXXX-XXXX | INDF     |                 | INDF uses co                                                                |                   |              |              | DIL 2    | DITI     | DIU      |  |

| 01h        | 0000-0000 | TMO      | Timer 0 Co      |                                                                             | Sintentis of 1 Si |              | ata memory   |          |          |          |  |

|            | 0000-0000 |          |                 | ounter [07]                                                                 |                   |              |              |          |          |          |  |

| 02h<br>03h | 0000-0000 | PC       | Flogram Co      |                                                                             | RAMBANK           |              |              | ZFLAG    | DCFLAG   | CFLAG    |  |

|            |           | STATUS   | <br>E Diana Eil |                                                                             |                   |              |              | ZFLAU    | DUFLAG   | CFLAG    |  |

| 04h        | 0000-0000 | FSR      |                 | e Select Regis                                                              |                   |              |              |          |          |          |  |

| 05h        | 0000-0000 | RSR      |                 | e Select Regi                                                               |                   |              |              |          |          |          |  |

| 06h        | 1111-1111 | PAD      |                 | A[07] Port A Pin data output register 3[03] Port B Pin data output register |                   |              |              |          |          |          |  |

| 07h        | 1111-1111 | PBD      |                 |                                                                             |                   |              |              |          |          |          |  |

| 08h        | 1111-1111 | PCD      |                 | [[07] Port C Pin data output register; Matrix Key Scan KSI [07]             |                   |              |              |          |          |          |  |

| 09h        | 1111-1111 | PDD      |                 | D[07] Port D Pin data output register; Matrix Key Scan KSO [07]             |                   |              |              |          |          |          |  |

| 0ah        | 1111-1111 | PED      | PE[07] Po       | [07] Port E Pin data output register; Matrix Key Scan KSO [815]             |                   |              |              |          |          |          |  |

| 0dh        | 0000-0000 | TM1      | TIMER 1 C       | MER 1 Counter                                                               |                   |              |              |          |          |          |  |

| 0eh        | xxxx-xxx0 | TM1IE    | TIMER1 In       | IMER1 Interrupt Enable TM1IE                                                |                   |              |              |          |          |          |  |

| 0fh        | xxxx-xxx0 | TM1IF    | TIMER1 In       | TIMER1 Interrupt flag, write 0 to clear it TM1I                             |                   |              |              |          |          |          |  |

| 10h        | 0000-0000 | USBE     | USBE            | USBE FUNADR                                                                 |                   |              |              |          |          |          |  |

| 11h        | 0000-0000 | INTFLAG1 | SET0I           | OUT0I                                                                       | TX0I              | TX1I         | TX2I         | SUSPI    | TX3I     | RC4I     |  |

| 12h        | x000-0000 | INTFLAG2 |                 | VDD5VRI                                                                     | WKTI              | RSTI         | RSMI         | KBDI     | PB0I     | TM0I     |  |

| 13h        | 0000-0xx0 | EPCFG    | SUSP            | RSMO                                                                        | EP1CFG            | EP2CFG       | DEVR         |          |          | OUT0RDY  |  |

| 14h        | 0000-0000 | EPOSET   | TX0RDY          | TX0TGL                                                                      | <b>EPOSTALL</b>   | IN0STALL     |              | TX0C     | NT[03]   |          |  |

| 15h        | 000x-0000 | EP1SET   | TX1RDY          | TX1TGL                                                                      | EP1STALL          |              |              | TX1C     | NT[03]   |          |  |

| 16h        | 000x-0000 | EP2SET   | TX2RDY          | TX2TGL                                                                      | EP2STALL          |              |              | TX2C     | NT[03]   |          |  |

| 17h        | 000x-0000 | EP3SET   | TX3RDY          | TX3TGL                                                                      | EP3STALL          | EP3CFG       |              |          |          |          |  |

| 18h        | 0x00-0xxx | EP4SET   | RC4RDY          | RC4TGL                                                                      | EP4STALL          | EP4CFG       | RC4ERR       |          |          |          |  |

| 19h        | x000-0000 | TX3CNT   | Endpoint 3      | transmit byte                                                               | count             |              |              |          |          |          |  |

| 1ah        | x000-0000 | RC4CNT   | Endpoint 4      | transmit byte                                                               | count             |              |              |          |          |          |  |

| 1bh        | 0010-0000 | 180CON   |                 |                                                                             |                   |              | I80BUSY      | I80EN    | I80START | I80DIR   |  |

| 1ch        | 0000-0000 | XRAMCON  |                 |                                                                             | SRAM1USB          | SRAM2USB     | SRAM1SPI     | SRAM2SPI | SRAM1I80 | SRAM2I80 |  |

| 1dh        | 0000-0000 | SPISET   |                 |                                                                             | SPIMODE           | SPIEN        | LSBFIRST     | SPIIN    | SPISW    | CLRADR   |  |

| 20h        | XXXX-XXXX | BANKO    |                 | 1                                                                           | Int               | ernal RAM 90 | 5 Bytes (BAN | K0)      | 1        |          |  |

| :<br>7fh   | xxxx-xxxx | BANK1    |                 |                                                                             | Int               | ernal RAM 90 | 6 Bytes (BAN | K1)      |          |          |  |

## **2.3** Data Memory Map (R-Plane)

| Addr            | RST       | NAME     | Bit 7        | Bit 6                            | Bit 5          | Bit 4        | Bit 3        | Bit 2         | Bit 1   | Bit 0  |  |  |  |

|-----------------|-----------|----------|--------------|----------------------------------|----------------|--------------|--------------|---------------|---------|--------|--|--|--|

| 00h             | XXXX-XXXX | INDR     | Addressing   | INDR uses co                     | ontents of RS  | R to address | data memory  |               | •       | •      |  |  |  |

| 01h             | 0000-0000 | TM0RLD   | Timer0 over  | flow reload v                    | value          |              |              |               |         |        |  |  |  |

| 02h             | 0000-0000 | TM0SET   |              |                                  |                | TM0EN        |              | TM0P          | SC[03]  |        |  |  |  |

| 03h             | XXXX-XXXX | PWRDOWN  | Write this R | egister to ent                   | er Power-Dov   | wn Mode      | •            |               |         |        |  |  |  |

| 04h             | 0000-0000 | WDTE     |              | -                                | r WDT and e    |              |              |               |         |        |  |  |  |

| 05h             | 0000-0000 | KBDMASK  |              |                                  | function while |              |              |               |         |        |  |  |  |

| 06h             | 0000-000x | WRCPD    | WRCPD        | WDT                              | FPSC           | WKT          |              | 5VINFLG       | OUTFLG  |        |  |  |  |

| 07h             | xx01-1000 | CLKSEL   |              |                                  | HWAUTO         | FCLKEN       | SCLKEN       | CLKSEL        |         | KDIV   |  |  |  |

| 09h             | xxxx-xx00 | IRCCKO   |              |                                  |                | -            | _            |               | PE3CKO  | PE3SEL |  |  |  |

| 0ah             | xx00-0000 | TM1EN    |              |                                  | TM1EN          | TM1SEL       |              | TM            | 1PSC    |        |  |  |  |

| 0eh             | x000-x000 | TKE      |              | TKE                              | TKSPI          | r            |              |               | TKSEL[2 |        |  |  |  |

| 11h             | 0000-0000 | USBINTEN | SET0IE       | OUT0IE                           | TX0IE          | TX1IE        | TX2IE        | SUSPIE        | TX3IE   | RC4IE  |  |  |  |

| 12h             | x000-0000 | FUNINTEN |              | VDD5VIE                          | WKTIE          | RSTIE        | RSMIE        | KBDIE         | PB0IE   | TM0IE  |  |  |  |

| 13h             | XXXX-XXXX | RC0SET   | RC0TGL       |                                  |                |              |              |               |         |        |  |  |  |

| 20h             | 0000-0000 | PAE      |              | 07] CMOS push-pull output enable |                |              |              |               |         |        |  |  |  |

| 21h             | xxxx-0000 | PBE      |              |                                  |                |              |              |               |         |        |  |  |  |

| 22h             | 0000-0000 | PCE      |              |                                  | ll output enab |              |              |               |         |        |  |  |  |

| 23h             | 0000-0000 | PDE      |              | .7] CMOS push-pull output enable |                |              |              |               |         |        |  |  |  |

| 24h             | 0000-0000 | PEE      |              | 07] CMOS push-pull output enable |                |              |              |               |         |        |  |  |  |

| 25h             | 0000-0000 | PAPU     |              | 07] pull-up , enable=0           |                |              |              |               |         |        |  |  |  |

| 26h             | 0000-0000 | PBPU     | PB[03] pul   | 3[03] pull-up , enable=0         |                |              |              |               |         |        |  |  |  |

| 27h             | xxxx-x000 | PCDEPU   |              | PCPU PDPU PEPU                   |                |              |              |               |         |        |  |  |  |

| 30h             | xxxx-x000 | PWMENF   |              | PWMPSC PWMEN                     |                |              |              |               |         |        |  |  |  |

| 31h             | 0000-0000 | PWMDUTY  | PWM DUT      | Y                                |                |              |              |               |         |        |  |  |  |

| 32h             | 0000-0000 | PWMPRD   | PWM Perio    |                                  |                |              |              |               |         |        |  |  |  |

| 3ah             | x000-0000 | I80LEN   | I80 DMA tr   | ansfer length                    |                |              | _            |               |         |        |  |  |  |

| 3bh             | xx00-0000 | SPIENF   |              |                                  | CPOL           | CPHA         |              |               | L[03]   |        |  |  |  |

| 3ch             | x000-0000 | SPICRS   |              |                                  |                |              | S[06] SPI C  |               |         |        |  |  |  |

| 3dh             | x000-0000 | SPILEN   |              |                                  |                |              | [06] SPI Tra | ansfer length |         |        |  |  |  |

| 3eh             | 0000-0000 | SPITX    |              |                                  | it DATA in C   | MD phase     |              |               |         |        |  |  |  |

| 3fh             | XXXX-XXXX | SPIRX    | SPIRX[07]    | ] SPI Receive                    | ed DATA        |              |              |               |         |        |  |  |  |

| 40h<br>:<br>47h | XXXX-XXXX | SET0FIFO | Endpoint 0   | SETUP Recei                      | ive Buffer (8  | Bytes)       |              |               |         |        |  |  |  |

| 48h<br>:<br>4fh | xxxx-xxxx | OUT0FIFO | Endpoint 1   | OUT Receive                      | e Buffer (8 By | tes)         |              |               |         |        |  |  |  |

| 50h<br>:<br>57h | xxxx-xxxx | TX0FIFO  | Endpoint 0'  | Transmit Buf                     | fer (8 Bytes)  |              |              |               |         |        |  |  |  |

| 58h<br>:<br>5fh | xxxx-xxxx | TX1FIFO  | Endpoint 1   | Transmit Buf                     | fer (8 Bytes)  |              |              |               |         |        |  |  |  |

| 60h<br>:<br>67h | xxxx-xxxx | TX2FIFO  | Endpoint 2   | Transmit Buf                     | fer (8 Bytes)  |              |              |               |         |        |  |  |  |

| 80h<br>:<br>bfh | xxxx-xxxx | XRAM1    | Endpoint 3/4 | 4 Buffer (64 l                   | Bytes)         |              |              |               |         |        |  |  |  |

| c0h<br>:<br>ffh | xxxx-xxxx | XRAM2    | Endpoint 3/4 | 4 Buffer (64 l                   | Bytes)         |              |              |               |         |        |  |  |  |

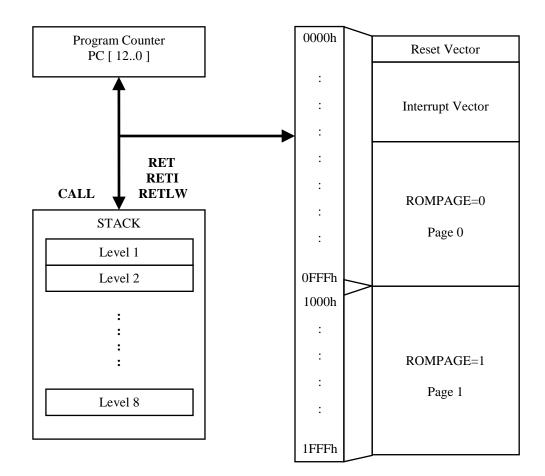

#### 2.4 Program Counter (PC) and Stack

The TM3130 has 13-bit Program Counter which is wide capable of addressing an 8K x 14 program Flash ROM. Program Counter (PC) keeps track of the program execution by holding the address of the current instruction. It is automatically incremented to the next instruction during the current instruction execution. The PC value is normally increasing as a program instruction is executed, the PC will contain the address of the next program instruction to be executed. The PC value is normally increased by one except the followings. The Reset and the Interrupt Vectors are provided for PC initialization and Interrupts. For CALL/GOTO instructions, PC loads the lower 12 bits address from instruction word and MSB from STATUS's bit 7 - ROMPAGE. For RET/RETI/RETLW instructions, PC retrieves its content from the top level of STACK. For the other instructions updating PC [7:0], the PC [12:8] keeps unchanged.

TMU3130 has a hardware call stack, which is used to save return addresses. TMU313 series has 13-bit wide and 8-level in depth. The Stack space is not part of either program or data space and the stack pointer is not readable or writable. The CALL instruction is used to jump to a subroutine program, and then it must be terminated with the RETURN instruction. When the CALL instruction is executed, the destination address is saved to the RISC. The RISC will "PUSH" destination address into the Stack when a CALL instruction is executed, or an interrupt causes a branch. The Stack is "POP" in the event of a RETURN, RETLW or a RETFIE instruction execution. The CALL instruction is used to jump to a subroutine program, which must be terminated with the RETURN, RETLW or a RETFIE instruction.

| ; Function: Sam |                 | Counter and Lookup table         |

|-----------------|-----------------|----------------------------------|

| ,               | . 0             |                                  |

| Start:          |                 |                                  |

| •               |                 |                                  |

| movfw           | TableCNT        | ; Set lookup table's adds        |

| call            | DeviceDescTable | · · ·                            |

| •               |                 |                                  |

| •               | 0.001           |                                  |

| org<br>.TABLE   | 0a00h           | ; Set lookup table start address |

| DeviceDescTabl  | ۵.              |                                  |

|                 | PCL,F           | ; Lookup adds W to the PCL       |

| String_Descript |                 | ; Lookup usus in to the rel      |

| retlw           | 'T'             |                                  |

| retlw           | ' <b>E</b> '    |                                  |

| retlw           | 'N'             |                                  |

| retlw           | 'X'             |                                  |

| •               |                 |                                  |

|                 |                 |                                  |

| END             |                 | ; End of user program            |

|                 |                 |                                  |

#### 2.5 Dual Clock and Clock Control Register

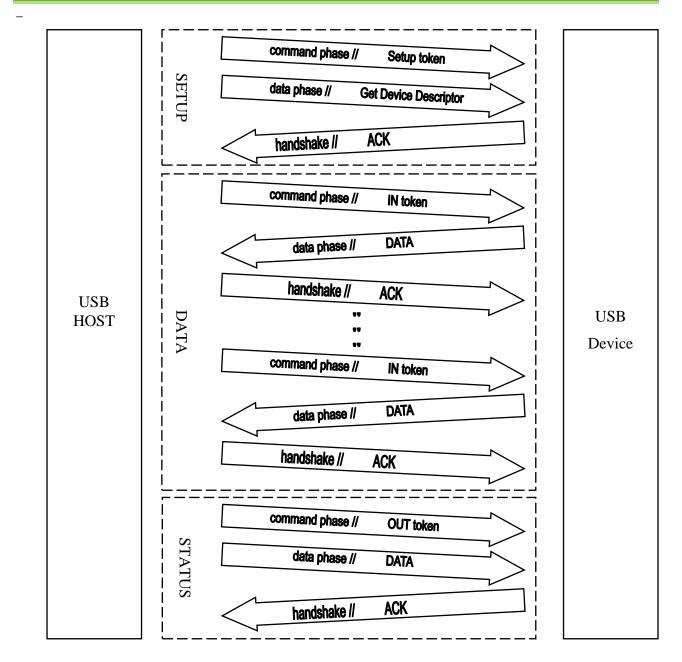

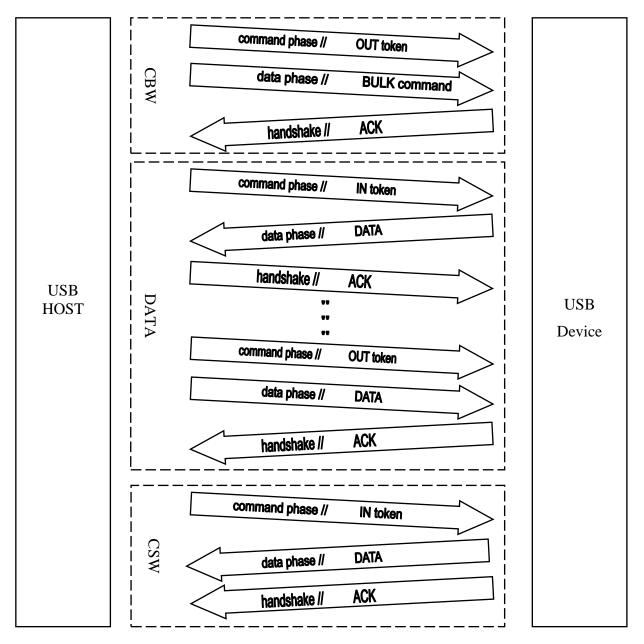

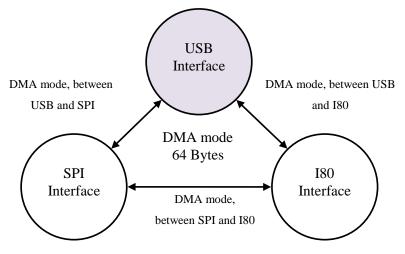

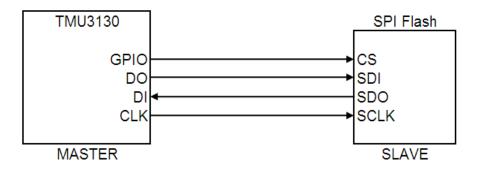

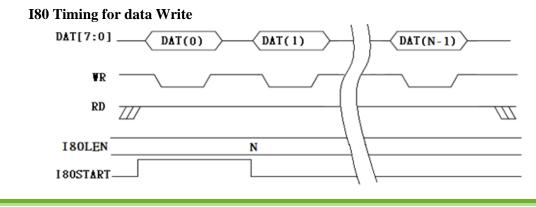

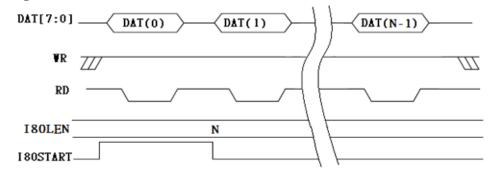

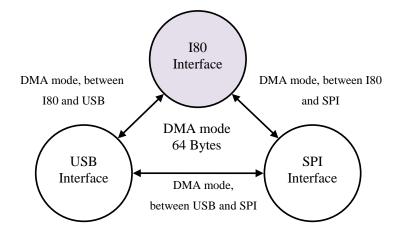

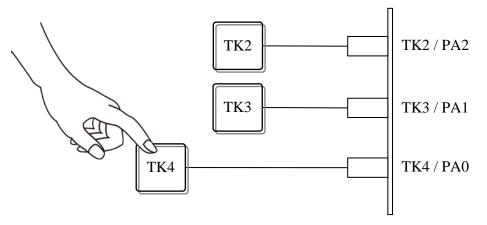

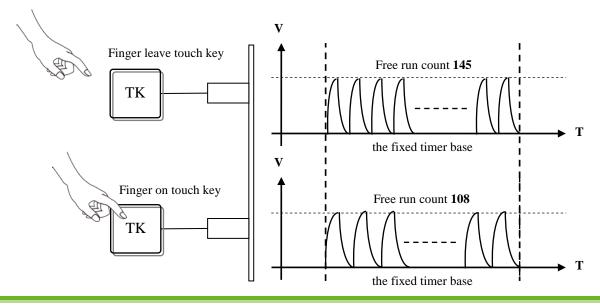

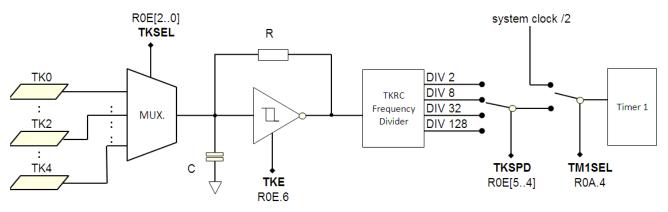

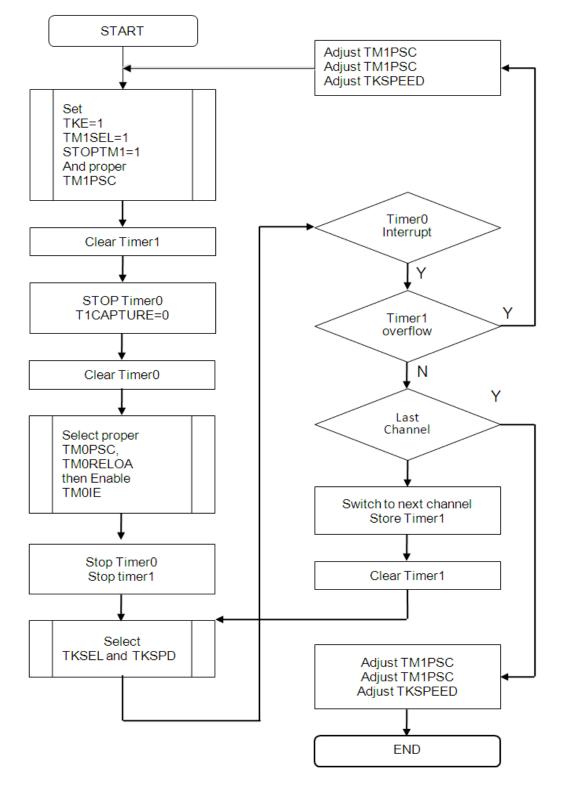

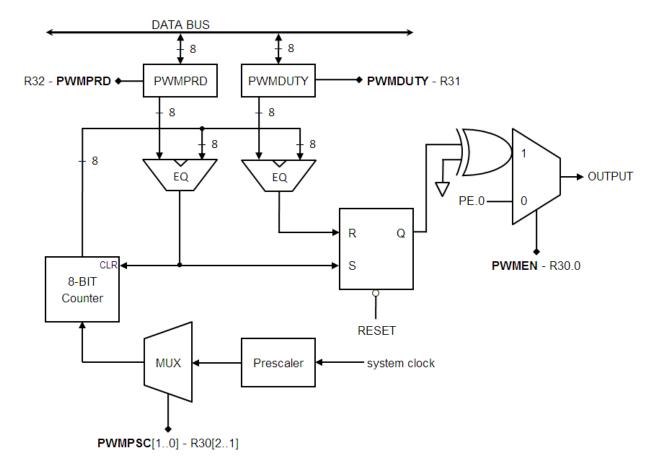

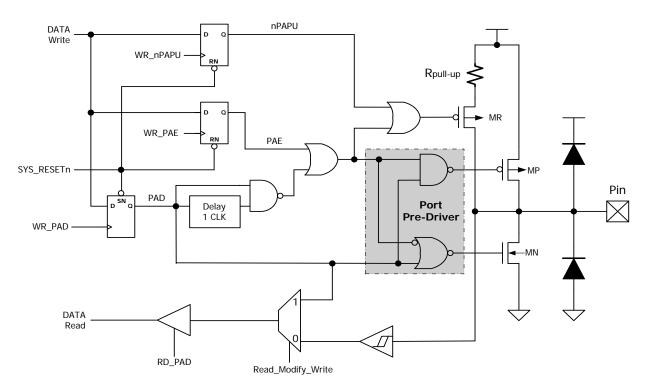

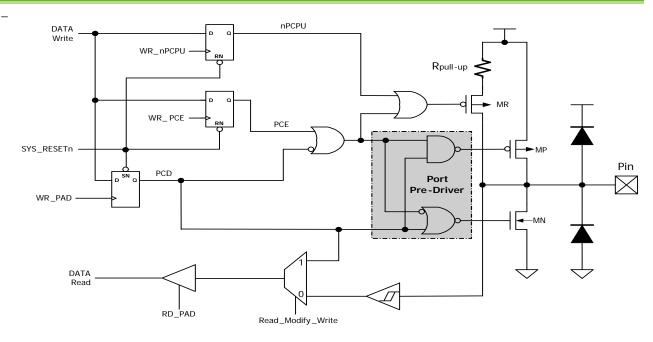

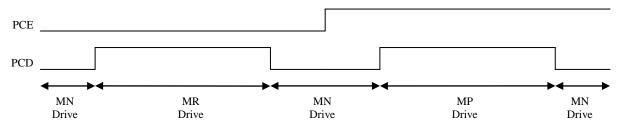

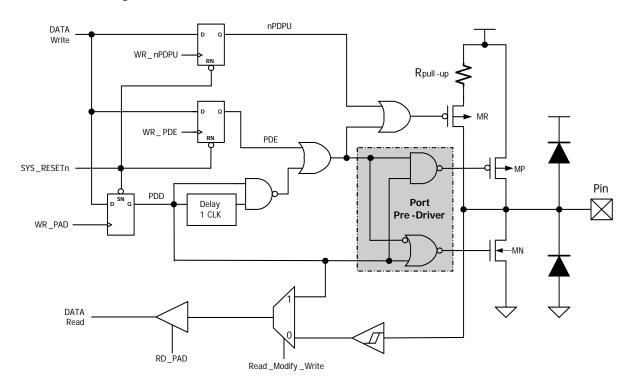

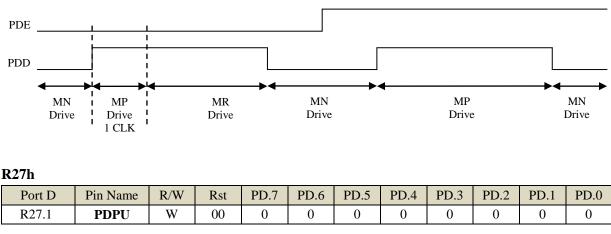

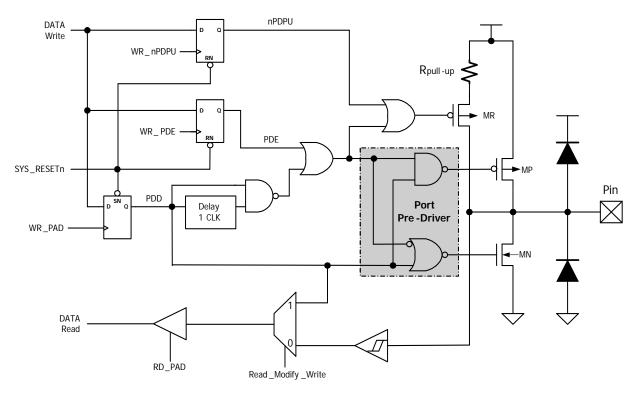

The TMU3130 has multiple system clocks; the RC oscillator (24 MHz) module is the master clock generator that supplies the system clock for the RISC, RAM, ROM and all of the peripheral modules using either an external crystal oscillator (6 MHz) or an internal RC oscillator. The external crystal oscillator operates with a 6 MHz crystal.